## Sierra Components, Inc.

2222 Park Place Building 3 Suite E • Minden, Nevada 89423

Phone: 775.783.4940 Fax: 775.783.4947

Chip back potential is the level which bulk silicon is maintained by on-chip connection, or it is the level to which the chip back must be connected when specifically stated below. If no potential is given the chip back should be isolated.

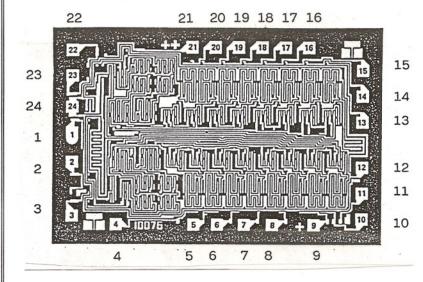

| Pad                             | <u>Function</u>                                    | Pad                             | <u>Function</u>                            | Pad                                    | <u>Function</u>                     |

|---------------------------------|----------------------------------------------------|---------------------------------|--------------------------------------------|----------------------------------------|-------------------------------------|

| 1<br>2<br>3<br>4<br>5<br>6<br>7 | Strobe<br>Data 1<br>Data 2<br>S7<br>S6<br>S5<br>S4 | 9<br>10<br>11<br>12<br>13<br>14 | S1<br>S2<br>S0<br>VSS<br>S13<br>S12<br>S15 | 17<br>18<br>19<br>20<br>21<br>22<br>23 | S9 S8 S11 S10 Data 3 Data 4 Inhibit |

| - 8                             | \$3                                                | 16                              | \$14                                       | 24                                     | VDD                                 |

Topside Metal: Al Backside: Si

**Backside Potential: VDD**

Mask Ref: 10076

Bond Pads (Mils): 4mils sq.

APPROVED BY:

MFG: Harris

**DIE SIZE (Mils):** 113 x 75

**THICKNESS: 20mils**

**DATE: 3/13/00**

P/N: CD4515BH

DG 10.1.2 Rev A 3-4-99